### Proceedings of the

## EMerging Technology (EMiT) Conference 2019

9-11 April 2019 University of Huddersfield, U.K.

## Edited by M.K. Bane and V. Holmes

### **Sponsors:**

https://emit.tech

9th-11th April, Huddersfield, UK

Welcome to Huddersfield and the fifth Emerging Tech conference.

Building upon events in Manchester and Barcelona during the last 5 years, EMiT continues to explore the challenges of hardware, software, tools and algorithms that are coming over the horizon or that the EMiT community is helping create itself. As this year's conference will explore, opportunities are opening via quantum and neuromorphic computing, with still a large number of challenges posed by machine learning as well as new possibilities for likes of FPGA, GPU and CPU programming. As the keynotes will discuss, we cannot treat hardware in isolation; to maximise our research and R&D (both in academia and industry) we need to take a holistic (co-design) approach and actively consider which emerging techniques may best accelerate our work, and particularly the intersection of new hardware and new techniques.

EMiT is more than a yearly conference. With an active Twitter account (@emit2019) and LinkedIn group, we promote dialogue on all the EMiT themes, as well as provide links and updates on relevant news and research. We aim to expand on this in coming months by building up reference materials on topics suggested by our members. But rather than get ahead of ourselves, we hope you enjoy this year's conference, use both these proceedings and the forthcoming IET publications and share your experiences using the hashtag #EMiT2019

EMiT2019 will be held at The University of Huddersfield in the United Kingdom. The University of Huddersfield has a long history of innovation and supporting emerging technologies. In 2012, it was named the Times Higher Education Entrepreneurial University of the Year and in 2013, Professor Elizabeth Towns-Andrews, the University's 3M Professor of Innovation, won the Queen's Award for Enterprise Promotion. In April 2017, The University of Huddersfield joined the Times Higher Education's world top 200 "young universities".

The Organising Committee has worked hard to realise EMiT2019, so please join us in extending your appreciation to each of them. We would also like to thank each keynote, everybody submitting papers or posters (accepted or not), as well as our sponsors, stall holders and the Yorkshire Sculpture Park, for showing their support to the EMiT series.

We are looking towards EMiT2020 so if you are inspired by this year's conference, either to host or join the Organising Committee, please do speak to us in person or email us at info@emit.tech

Yours,

EMiT (https://emit.tech)

1) Holmes

Violeta Holmes, the University of Huddersfield

Michael Bane, High End Compute Ltd (https://highendcompute.co.uk)

### **EMiT2019 Local Organising Committee**

Dr. Violeta Holmes

University of Huddersfield

Dr. Anju P. Johnson

University of Huddersfield

Dr. Faheem A. Khan

University of Huddersfield

Dr. Mahmoud Dhimish

University of Huddersfield

Ms. Rebecca Marsden

University of Huddersfield

### **EMiT2019 Local Organising Committee**

Dr. Michael K. Bane High End Compute Ltd

Dr. Stephen Longshaw STFC

Prof. Benedict Rogers

Dr. David Topping

Dr. Javier Navaridas

University of Manchester

University of Manchester

University of Manchester

### **EMiT2019 Advisory Panel**

Prof. Jack Dongarra University of Tennessee

Dr. Kirk E. Jordan IBM

### **Printing**

The EMiT2019 committees shall not be held responsible for any statement or opinion advanced in papers or otherwise printed in this volume. Authors' papers have been prepared for final reproduction/printing from supplied PDFs without any changes and the authors are fully responsible for information contained in their papers.

Copyright © Michael Bane, EMiT (Emerging Tech) Conference series

Published by

EMiT/University of Huddersfield/High End Compute Ltd/University of Manchester

**Proceedings of the 2019 Emerging Technology Conference**

9-11 April 2019, University of Huddersfield, Huddersfield, U.K.

ISBN: 978-0-9933426-4-6

#### Day 1- Tuesday 9th April 2019

The first day of EMiT 2019 is dedicated to two technical workshops that will run in parallel.

- Deep Learning workshop using both NVIDIA GPUs and a new Neuromorphic platform called SpiNNaker via a software toolchain called SPANNER. A laptop will be required for this workshop.

Quantum computing workshop delivered by IBM Research. This will provide a mixture of taught and practical elements, including use of real quantum hardware. Bring your own laptop or a number of fixed workstations will be available on a first come, first served basis.

#### Day 2 - Wednesday 10th April 2019

| Day 2 - Wedn  | lesday 10th April 2019                                                                                                                                                |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 08:00 - 09:30 | Registration and Refreshments                                                                                                                                         |  |  |  |

| 09:30 - 10:00 | Conference Introductions                                                                                                                                              |  |  |  |

| (15 minutes)  | Welcome to the conference and introduction to EMIT 2019   Dr Violeta Holmes,<br>University of Huddersfield                                                            |  |  |  |

| (15 minutes)  | Welcome from the Director of Research and Enterprise at Huddersfield,<br>Prof Liz Towns-Andrews                                                                       |  |  |  |

| 10:00 - 10:45 | Keynote Presentation: Prof. Veljko Milutinovic, Indiana University DataFlow SuperComputing for Big Data Analytics                                                     |  |  |  |

| 10:45 - 11:10 | Break & Posters                                                                                                                                                       |  |  |  |

| 11:10 - 12:10 | Session 1: Novel Hardware                                                                                                                                             |  |  |  |

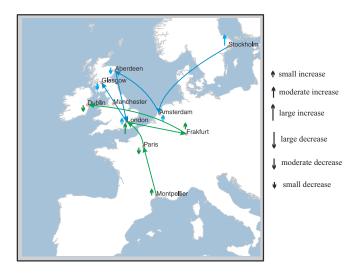

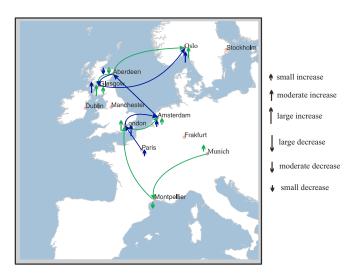

| (20 minutes)  | M. Ashworth, G. Riley, A. Attwood & J. Mawer Prospects for Low-power Acceleration of HPC Workloads in EuroExa: FPGA Acceleration of a Numerical Weather Forecast Code |  |  |  |

| (20 minutes)  | J. Lant & J. Navaridas Direct Communication between Distributed FPGA Resources                                                                                        |  |  |  |

| (20 minutes)  | P. A. Bogdan, G. P. Garcia, S. Davidson, M. Hopkins, R. James & S. Furber<br>Event-based computation: Unsupervised elementary motion decomposition                    |  |  |  |

| 12:10 - 13:10 | Lunch & Posters                                                                                                                                                       |  |  |  |

| 13:10 - 14:30 | Session 2: Deep Learning                                                                                                                                              |  |  |  |

| (20 minutes)  | S. Al-Riyami<br>An efficient way to deal with algorithmically generated data in deep learning                                                                         |  |  |  |

| (20 minutes)  | M. Seedall, V. Holmes & K. Macfarlane<br>SafeChat System with NLP and DNN                                                                                             |  |  |  |

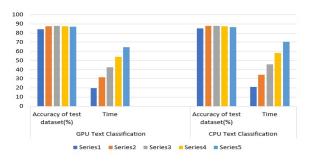

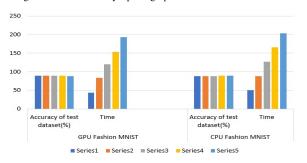

| (20 minutes)  | A. W. Qurashi & V. Holmes     Comparison of Deep Neural Network approach in text and image classification using     CPU and GPU systems                               |  |  |  |

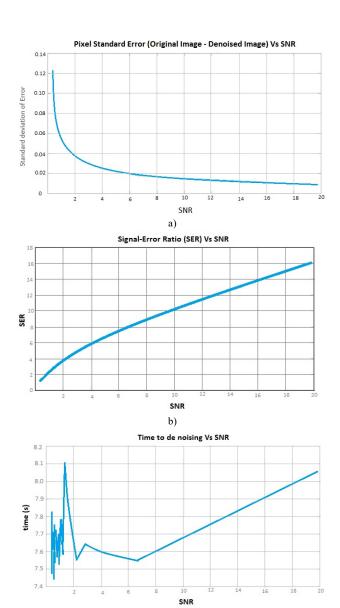

| (20 minutes)  | H. Alattal, F. Khan & Q. Ahmed<br>Denoising an Image Using Deep Learning Techniques                                                                                   |  |  |  |

| 14:30 - 15:00 | Break & Posters                                                                                                                                                       |  |  |  |

| 15:00 - 16:00 | Session 3: GPU Computing                                                                                                                                              |  |  |  |

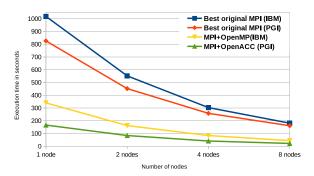

| (20 minutes)  | J. Grasset, Y. Audouin, S. Longshaw, C. Moulinec and D. Emerson<br>Porting and Optimising TELEMAC-MASCARET for the OpenPOWER Ecosystem                                |  |  |  |

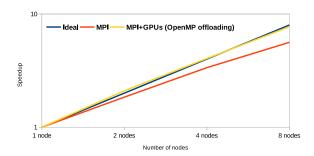

| (20 minutes)  | M. Turchetto, R. Vacondio and A. Dal Palù<br>Multi-GPU implementation of a 2D Shallow Water Equations Solver over a<br>Multi-Resolution grid                          |  |  |  |

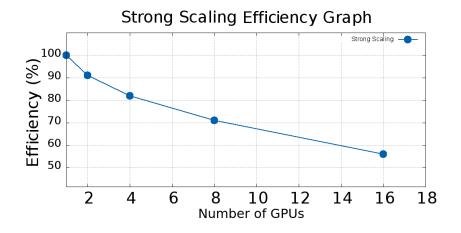

| (20 minutes)  | V. Stegailov, N. Kondratyuk, G. Smirnov and A. Timofeev<br>The Desmos supercomputer for computational materials science                                               |  |  |  |

| 16:30 - 23:00 | Visit to Yorkshire Sculpture Park and evening banquet meal (including travel from and to The University of Huddersfield)                                              |  |  |  |

#### Day 3 - Thursday 11th April 2019

| 08:00 - 09:00 | Registration and Refreshments                                                                                                                             |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 09:00 - 09:45 | Keynote Presentation: Dr Torsten Hoefler, ETH Zurich                                                                                                      |  |  |  |  |  |

|               | High-Performance Communication in Machine Learning                                                                                                        |  |  |  |  |  |

| 09:50 - 10:30 | Session 4: Novel Communication Systems                                                                                                                    |  |  |  |  |  |

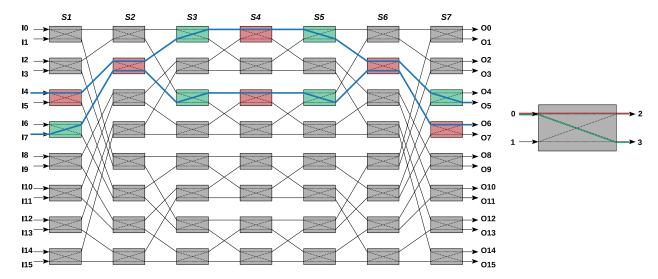

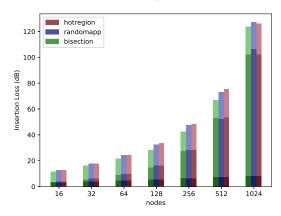

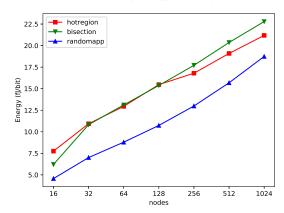

| (20 minutes)  | M. Kynigos, J. Navaridas and J. A. Pascual<br>Scalability of a Silicon Photonic Switch for High-Performance Interconnects                                 |  |  |  |  |  |

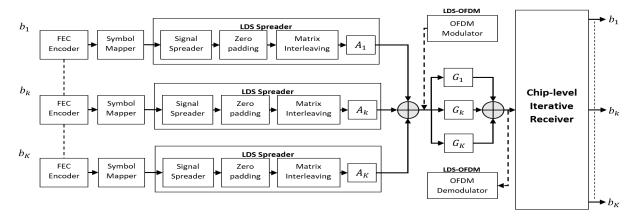

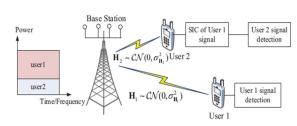

| (20 minutes)  | Z. Elsaraf, F. Khan and Q. Ahmed<br>Performance Analysis of Code-Domain NOMA in 5G Communication Systems                                                  |  |  |  |  |  |

| 10:30 - 11:00 | Break & Posters                                                                                                                                           |  |  |  |  |  |

| 11:00 - 12:30 | Keynote Presentation & Panel Discussion                                                                                                                   |  |  |  |  |  |

| (45 minutes)  | Dr Peter Hopton, ICEOTOPE Hardware and Infrastructure Technology Challenges to Achieving ExaScale – and EuroEXA's Answer                                  |  |  |  |  |  |

| (40 minutes)  | Chaired Panel Discussion                                                                                                                                  |  |  |  |  |  |

| 12:30 - 13:30 | Lunch & Posters                                                                                                                                           |  |  |  |  |  |

| 13:30 - 14:30 | Session 5: Novel Software                                                                                                                                 |  |  |  |  |  |

| (20 minutes)  | L. Ragta, J. Meng, X. Gu and D. Emerson<br>A high level abstraction approach for lattice Boltzmann simulations using future<br>computing systems          |  |  |  |  |  |

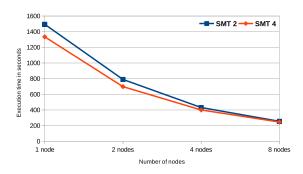

| (20 minutes)  | S. Titarenko, V. Titarenko, G. Aivaliotis and J. Palczewski Constraint-based frequent pattern mining algorithm and its optimisation for multicore systems |  |  |  |  |  |

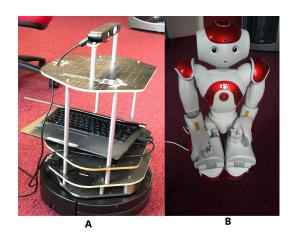

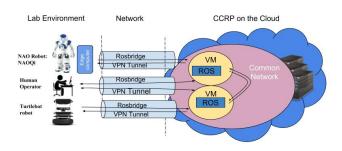

| (20 minutes)  | H. Aagela and V. Holmes<br>Cloud Robotics-Based System for Robot Teleoperation                                                                            |  |  |  |  |  |

| 14:30 - 15:00 | Break & Posters                                                                                                                                           |  |  |  |  |  |

| 15:00 - 16:00 | Session 6: Applications of Emerging Tech                                                                                                                  |  |  |  |  |  |

| (20 minutes)  | M. Vallati and A. Grassi<br>Al to Facilitate Legal Analysis in the PESTLE Context                                                                         |  |  |  |  |  |

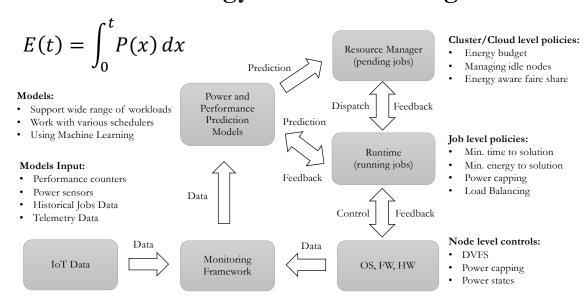

| (20 minutes)  | V. Elisseev<br>Holistic Approach to Energy and Power Management in HPC                                                                                    |  |  |  |  |  |

| (20 minutes)  | H. Aagela and V. Holmes     Collaborative Cloud-based Face recognition approach for Humanoid robots                                                       |  |  |  |  |  |

| 16:00 - 16:30 | Conference Summary & Close                                                                                                                                |  |  |  |  |  |

|               |                                                                                                                                                           |  |  |  |  |  |

## EMiT | 20 19

**Emerging Technology Conference**

## University of HUDDERSFIELD

Inspiring global professionals

EMIT2019 Emerging Technologies Conference in being within the University of Huddersfield.

Huddersfield is a large market town in West Yorkshire, England. It is the 11th largest town in the UK, with a population of over 162k. Huddersfield itself is a town of Victorian architecture. The railway station is a Grade I listed building described by John Betjeman as "the most splendid station façade in England", second only to St Pancras, London. The station in St George's Square was renovated at a cost of £4million and subsequently won the Europa Nostra award for European architecture.

Huddersfield is within the historic county boundaries of the West Riding of Yorkshire, it is the largest urban area in the metropolitan borough of Kirklees. The town is known for its role in the Industrial Revolution, and for being the birthplaces of rugby league, the Labour Prime Minister Harold Wilson, and the film star James Mason.

Close by is the famous Brontë Country that is less than an hour drive from Huddersfield. The name comes from the Brontë sisters, who wrote such literary classics as Jane Eyre, Wuthering Heights, and The Tenant of Wildfell Hall, while living in the area.

The Yorkshire Sculpture Park who will host the conference banquet dinner, is set in beautiful fields, hills, woodland, lakes and formal gardens combined to create a beautiful landscape and stunning setting

We sincerely hope you will join us in being part of this exciting event.

### **CONTENTS**

| KEYNOTE LECTURES                                                                                                                                                                                                                | 9  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| DataFlow SuperComputing for Big Data Analytics V. Milutinovic                                                                                                                                                                   | 9  |

| High-Performance Communication in Machine Learning T. Hoefter                                                                                                                                                                   | 10 |

| PEER REVIEWED PAPERS                                                                                                                                                                                                            | 11 |

| Session 1: Novel Hardware  Prospects for Low-power Acceleration of HPC Workloads in EuroExa: FPGA Acceleration of a Numerical Weather Forecast Code                                                                             | 12 |

| M. Ashworth, G. Riley, A. Attwood, J. Mawer                                                                                                                                                                                     |    |

| J. Lant, J. Navaridas  Event-based computation: Unsupervised elementary motion decomposition  P.A. Bogan, G.P. Garcia, S. Davidson, R. Hopkins, R. James, S. Furber                                                             |    |

| Session 2: Deep Learning                                                                                                                                                                                                        | 25 |

| An efficient way to deal with algorithmically generated data in deep learning  S. Al-Riyami, A. Lisitsa, F. Coenen                                                                                                              | 25 |

| SafeChat System with NLP and DNN  M. Seedall, V. Holmes, K. Macfarlane  Comparison of Deep Neural Network approach in text and image classification using CPU and GPU systems                                                   | 28 |

| A.W. Qurashi, V. Holmes                                                                                                                                                                                                         |    |

| H. Alattal, F. Khan, Q. Ahmed                                                                                                                                                                                                   | 36 |

| Session 3: GPU Computing                                                                                                                                                                                                        | 41 |

| Porting and Optimising TELEMAC-MASCARET for the OpenPOWER Ecosystem  J. Grasset, Y. Audouin, S. Longshaw, C. Moulinec, D. Emerson  Multi-GPU implementation of a 2D Shallow Water Equations Solver over a Multi-Resolution grid | 41 |

| M. Turchetto, R. Vacondio, A. Dal Palu  The Desmos supercomputer for computational materials science                                                                                                                            | 45 |

| V. Stegailov, N. Kondratyuk, G. Smirnov, A. Timofeev                                                                                                                                                                            | 46 |

| Session 4: Novel Communication Systems                                                                                                                                                                                          | 48 |

| Scalability of a Silicon Photonic Switch for High-Perfomance interconnects  M. Kynigos, J. Navaridas, J.A. Pascual  Performance Analysis of Code-Domain NOMA in 5G Communication Systems                                        | 48 |

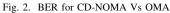

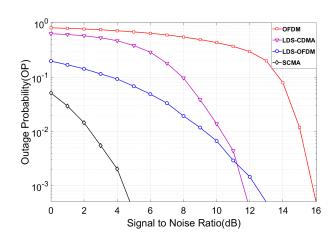

| Z. Elsaraf, F. Khan, Q. Ahmed                                                                                                                                                                                                   | 52 |

| Session 5: Novel Software                                                                                                                                                                                                       | 57 |

| A high level abstraction approach for Lattice Boltzmann simulations using future computing systems  L. Ragta, J. Meng, X. Gu, D. Emerson                                                                                        | 57 |

| Constraint-based frequent pattern mining algorithm and its optimisation for multicore systems  S. Titarenko, V. Titarentko, G. Aivaliotis, J. Palczewski                                                                        | 58 |

| Cloud Robotics-Based System for Robot Teleoperation  H. Aagela, V. Holmes                                                                                                                                                       | 62 |

| Session 6: Applications of Emerging Tech                                                                     | 66 |

|--------------------------------------------------------------------------------------------------------------|----|

| AI to Facilitate Legal Analysis in the PESTLE Context                                                        |    |

| M. Vallati, A. Grassi                                                                                        | 66 |

| Holistic Approach to Energy and Power Management in HPC                                                      |    |

| V. Elisseev                                                                                                  | 69 |

| Collaborative Cloud-based Face recognition approach for Humanoid robots                                      |    |

| H. Aagela, V. Holmes                                                                                         | 72 |

|                                                                                                              |    |

| POSTERS                                                                                                      | 76 |

| Black-box Tracking system for Drones using LoRa                                                              |    |

| H. Aagela, V. Holmes                                                                                         | 77 |

| Security Orchestration Automation and Response (SOAR) in High Performance Computing Systems                  |    |

| T. Al-Jofy, V. Holmes                                                                                        | 78 |

| Big Data One Millions Songs Dataset                                                                          |    |

| C. Arinto                                                                                                    | 79 |

| High End Compute                                                                                             |    |

| M.K. Bane                                                                                                    | 80 |

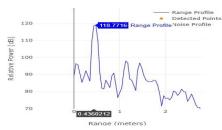

| Indoor Two Way Ranging using mm-Wave for Future Wireless Networks                                            |    |

| A. Farooq, Q. Ahmed, F. Khan and T. Alade                                                                    | 81 |

| Tunable Fault Tolerant Spiking Neural Networks on FPGAs                                                      |    |

| A.P. Johnson, J. Liu, A.G. Millard, S. Karim, A.M. Tyrrell, J. Harkin, J. Timmis, L. McDaid and              |    |

| D.M. Halliday                                                                                                | 82 |

| RISC-V Implementation                                                                                        |    |

| J. Parkinson                                                                                                 | 83 |

| Energy harvesting promising sign for advanced 5G wireless communication network and Internet of Things (IoT) |    |

| based storage devices                                                                                        |    |

| J. Yazdani and V. Thayananthan                                                                               | 84 |

## **KEYNOTE LECTURES**

## DataFlow SuperComputing for Big Data Analytics

Prof. Veljko Milutinovic Indiana University

Abstract—This presentation analyses the essence of DataFlow SuperComputing, defines its advantages and sheds light on the related programming model. DataFlow computers, compared to ControlFlow computers, offer speedups of 20 to 200 (even 2000 for some loops-intensive applications), power reductions of about 20, and size reductions of also about 20. However, the programming paradigm is different, and has to be mastered. The talk explains the paradigm, using Maxeler as an example, and sheds light on the ongoing research, which, in the case of the speaker, was highly influenced by four different Nobel Laureates: (a) from Richard Feynman it was learned that future computing paradigms will be successful only if the amount of data communications is minimized; (b) from Ilya Prigogine it was learned that the entropy of a computing system would be minimized if spatial and temporal data get decoupled; (c) from Daniel Kahneman it was learned that the system software should offer options related to approximate computing; and (d) from Andre Geim it was learned that the system software should be able to trade between latency and precision.

Prof. Veljko Milutinovic received his PhD from the University of Belgrade, spent about a decade on various faculty positions in the USA (mostly at Purdue University), and was a co-designer of the DARPAs first GaAs RISC microprocessor. Later, for almost 3 decades, he taught and conducted research at the University of Belgrade, in EE, MATH, BA, and PHYS/CHEM. Now he serves as the Chairman of the Board for the Maxeler operation in Belgrade, Serbia. His research is mostly in data-mining algorithms and data-flow computing, with the emphasis on mapping of data analytics algorithms onto fast energy efficient architectures. For 7 of his books, forewords were written by 7 different Nobel Laureates with whom he cooperated on his past industry sponsored projects. He has over 40 IEEE journal papers, over 40 papers in other SCI journals (4 in ACM journals), over 400 Thomson-Reuters citations, and about 4000 Google Scholar citations. Short courses on the subject he delivered so far in a number of universities worldwide: MIT, Harvard, Boston, NEU, Columbia, NYU, Princeton, Temple, Purdue, IU, UIUC, Michigan, EPFL, ETH, Karlsruhe, Heidelberg, Napoli, Salerno, Siena, Pisa, etc. Also at the World Bank in Washington DC, Brookhaven National Laboratory, IBM TJ Watson, Yahoo NY, ABB Zurich, Oracle Zurich, etc.

## High-Performance Communication in Machine Learning

Prof. Torsten Hoefler ETH Zurich

Abstract—One of the main drivers behind the rapid recent advances in machine learning has been the availability of efficient system support. Despite existing progress, scaling compute-intensive machine learning workloads to a large number of compute nodes is still a challenging task. In this talk, we provide an overview of communication aspects in deep learning. We address the communication challenge, by proposing SparCML, a general, scalable communication layer for machine learning applications. SparCML is built on the observation that many distributed machine learning algorithms either have naturally sparse communication patterns, or have updates which can be sparsified in a structured way for improved performance, without loss of convergence or accuracy. To exploit this insight, we analyze, design, and implement a set of communication-efficient protocols for sparse input data, in conjunction with efficient machine learning algorithms which can leverage these primitives. Our communication protocols generalize standard collective operations, by allowing processes to contribute sparse input data vectors, of heterogeneous sizes. Our generic communication layer is enriched with additional features, such as support for non-blocking (asynchronous) operations and support for low-precision data representations. We validate our algorithmic results experimentally on a range of large-scale machine learning applications and target architectures, showing that we can leverage sparsity for order-of-magnitude runtime savings, compared to existing methods and frameworks.

Dr Hoefler is an Associate Professor of Computer Science at ETH Zürich, Switzerland. Before joining ETH, he led the performance modelling and simulation efforts of parallel petascale applications for the NSF-funded Blue Waters project at NCSA/UIUC. He is also a key member of the Message Passing Interface (MPI) Forum where he chairs the "Collective Operations and Topologies" working group. Torsten won best paper awards at the ACM/IEEE Supercomputing Conference SC10, SC13, SC14, EuroMPI'13, HPDC'15, HPDC'16, IPDPS'15, and other conferences. He published numerous peerreviewed scientific conference and journal articles and authored chapters of the MPI-2.2 and MPI-3.0 standards. He received the Latsis prize of ETH Zurich as well as an ERC starting grant in 2015. His research interests revolve around the central topic of "Performance-centric System Design" and include scalable networks, parallel programming techniques, and performance modelling. Further details can be found on his home page at https://htor.inf.ethz.ch/

## PEER REVIEWED PAPERS

Session 1: Novel Hardware

# Prospects for Low-power Acceleration of HPC Workloads in EuroExa: FPGA Acceleration of a Numerical Weather Forecast Code

Mike Ashworth

School of Computer Science

University of Manchester

Manchester, United Kingdom

mike.ashworth.compsci@manchester.a

c.uk

Graham Riley

School of Computer Science

University of Manchester

Manchester, United Kingdom

graham.riley@manchester.ac.uk

Andrew Attwood

School of Computer Science

University of Manchester

Manchester, United Kingdom

andrew.attwood@manchester.ac.uk

John Mawer School of Computer Science University of Manchester Manchester, United Kingdom john.mawer@manchester.ac.uk

Abstract—The EuroExa project proposes a High-Performance Computing (HPC) architecture which is both scalable to Exascale performance levels and delivers worldleading power efficiency. This is achieved through the use of low-power ARM processors accelerated by closely-coupled FPGA programmable components. In order to demonstrate the efficacy of the design, the EuroExa project includes application porting work across a rich set of applications. One such application is the new weather and climate model, LFRic (named in honour of Lewis Fry Richardson), which is being developed by the UK Met Office and its partners for operational deployment in the middle of the next decade. Much of the runtime of the LFRic model consists of compute intensive operations which are suitable for acceleration using FPGAs. We have selected the Xilinx Vivado toolset including High-Level Synthesis (HLS) which generates IP blocks that can be combined with other standard IP blocks in Vivado Design Studio and a bitstream generated for programming the FPGA. A design using twelve matrix-vector IP blocks achieves 5.34 double precision Gflop/s. We shall discuss the implementation, the performance achieved and the prospects for acceleration of the full LFRic weather model.

Keywords—FPGA, High Level Synthesis, numerical weather forecasting

#### I. INTRODUCTION

Field Programmable Gate Arrays (FPGA) have attracted the attention of both academic and industry research as a mainstream accelerator for large-scale high-performance computing applications [1], for example in atmospheric simulations for weather forecasting [2]. The EuroExa project proposes a high-performance architecture which is both scalable to Exascale performance levels and delivers world-leading power efficiency. This is achieved through the use of low-power ARM processors accelerated by closely-coupled FPGA programmable components. In order to demonstrate the efficacy of the design, the EuroExa project includes application porting work across a rich set of applications.

One such application is the new weather and climate model, LFRic, which is being developed by the UK Met Office and its partners for operational deployment in the early part of the 2020 decade. The LFRic code is named in honour of Lewis Fry Richardson who in 1922 presented not only a detailed description of numerical weather forecasting but also

insights into how such a forecast could be carried out using parallel computing:

"A myriad computers are at work upon the weather of the part of the map where each sits, but each computer attends to only one equation or part of an equation. The work of each region is coordinated by an official of higher rank." [3]

High quality forecasting of the weather on global, regional and local scales is of great importance to a wide range of human activities. The UK Government funding in 2014 for new HPC systems at the Met Office was supported by a business case which anticipated £2 billion of economic impact for a £100 million investment – a Return on Investment of twenty [4][5]. Greater benefits come from increased accuracy, and exploitation of latest developments in HPC has always been of critical importance to the weather forecasting community.

LFRic is a new atmospheric model, being developed at the Met Office in the United Kingdom, which supports simulations for both weather forecasting and climate simulations. The current operational model at the Met Office, the Unified Model, uses a latitude-longitude grid in which lines of longitude converge at the poles leading to problems in performance and scalability, especially on modern highly parallel HPC systems. In a pre-cursor project between the Met Office, the Natural Environment Research Council and the Science and Technology Facilities Council, called GungHo, a new dynamical core was developed using the cube-sphere grid which covers the globe in a uniform way [6].

The GungHo code has also been developed specifically to maintain performance at high and low resolution and for high and low CPU core counts. A key technology to achieve this is Separation of Concerns, in which the science code is separated from the parallel, performance-related code and the PSyclone code generation tool is used to automatically generate code targeting different computer architectures. The LFRic weather and climate model is based on the GungHo dynamical core with its PSyclone software technology [7].

#### II. THE MATRIX-VECTOR KERNEL

Much of the run-time of the LFRic model consists of compute intensive operations which are suitable for acceleration using FPGAs, and many of those in the dynamics are based on matrix-vector products, for example in the Helmholtz solver. We have used the Xilinx Vivado toolset including High-Level Synthesis (HLS) to generate, from standard C code, bitstreams for programming the FPGA.

Vivado HLS generates a block of code for the FPGA (an IP block) from a pure C, C++ or OpenCL functions annotated with HLS pragmas, which supply optimization hints and instructions about the data interface. HLS also produces a synthesis report which contains optimization advice and performance metrics, most importantly the Task Latency.

Using this feedback from HLS is it possible to optimise the code without executing it, achieving a substantial reduction in the reported latency. Objectives of the optimization were

- to achieve streaming of data in and out of the IP block with a target of one 64-bit word per clock cycle;

- to achieve pipelining of the arithmetic operations and overlapping of multiplies with additions to achieve one 64-bit multiplication and one 64-bit addition every cycle; and

- to minimize use of resources on the FPGA.

The following optimizations were carried out:

- loops were swapped to make the index over the vertical levels the innermost loop;

- data arrays were transposed where necessary to ensure that data running over the vertical index were sequential in memory; together with the above this ensures a sequential innermost loop of length 40 elements;

- the HLS UNROLL pragma was applied to the innermost loops; unrolling by hand was also tried but shown to result in no additional benefit;

- the HLS PIPELINE pragma was applied to the outermost loop;

- the code just computes the matrix-vector product, without updating the left-hand side array; the update can be performed on the ARM CPU;

- HLS INTERFACE pragmas were added to define the interfaces for the subprogram arguments; in particular the clauses num\_read\_outstanding=8, max\_read\_burst\_length=64, num\_write\_outstanding=8, max\_write\_burst\_length=64, were used;

- data read from and written to the subprogram arguments were copied into and copied out from local working arrays using memcpy; and

- the input vector is constant for iterations of the outer loop, so it is copied in to its local array once at the start; at each iteration of the loop, slices of the matrix are copied in and columns of the output array are copied out.

The last two optimizations in the list above were particularly important. Without them data reads are not streamed, with each word being read independently as though the block is waiting for one read to complete before starting the next. With the optimizations, data is streaming at one word per cycle. We note in particular the benefit of the use of

memcpy; HLS recognises memcpy and implements it using "burst mode" [8].

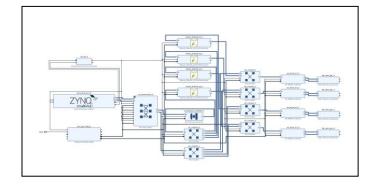

Matrix-vector IP blocks generated by HLS were combined with other standard IP blocks in Vivado Design Studio in order to provide functions in the design for data handling, interface with the ARM CPU, BRAM memories, clock control etc. A bitstream may then be generated for programming the FPGA. The design comprises the following:

- a ZynQ UltraScale+MPSoC IP block, which provides an interface to the ARM processor, through two master AXI4 High Performance Master Full Power Domain ports (HPM0 FPD and HPM1 FPD);

- a number, nblocks, of matrix-vector IP blocks;

- the same number, nblocks, of Block Memory Generator blocks to provide BRAM block memory, one memory block per matrix-vector block;

- the same number, nblocks, of AXI BRAM Controller blocks to provide an AXI protocol interface for each memory block;

- the same number, nblocks, of AXI Crossbar switches to allow both the matrix-vector blocks and the ZynQ to access the BRAMs;

- two AXI Crossbar switches to allow the two master ports on the ZynQ to fan out to (1) the slave ports on the BRAM memory controllers and (2) the slave ports on the matrix-vector blocks;

- an AXI Protocol block which provides conversion between AXI4 and AXI4LITE for the slave ports on the matrix-vector blocks;

- a Clocking Wizard IP block, which provides a custom clock and is used to vary the clock speed provided to the other blocks;

- a Processor Reset System block

An example of this design with four matrix-vector blocks is shown in Fig. 1.

The FPGA is then driven by standard C code on the ARM processor. FPGA memory is opened as a device on the ARM and mapped into user space. An area of memory referred to in Vivado as the "Control Registers" is used to control each IP block.

Fig. 1. The full design with four matrix-vector blocks and four BRAM memory blocks implemented in Vivado Design Suite

On the ARM side we load data into BRAM, set the addresses for the three arrays (two input and one output), start the block using the AP\_START bit, monitor the AP\_IDLE bit to check for completion, and copy output data from BRAM.

A matrix-vector kernel extracted from the LFRic code has been run on a Xilinx UltraScale+ ZCU102 Evaluation Platform [9]. At its heart this board contains a Multi-Processor System-on-Chip (MPSoC) comprising, in addition to other processors, an ARM Cortex A53 quad-core CPU running at 1.2 GHz and a ZynQ UltraScale XCZU9EG-FFVB1156 FPGA. The FPGA contains some 600k logic cells, 2,520 DSP slices and around 3.5 MB of BRAM memory. The ARM CPU is running Ubuntu 14.04.5 and we are using Vivado Design Suite and Vivado HLS, both at version level 2017.4, to generate IP blocks and bitstreams for the FPGA.

Performance of the matrix-vector code was timed, excluding the data transfers between the ARM CPU and the FPGA. The reason for this is that whether data is transferred depends on the context. The major part of this data set, 17MB out of 19MB, consists of the matrices. In any completed port of the LFRic weather model to the FPGA system, the matrices will be generated and used on the FPGA and so will never need to be transferred.

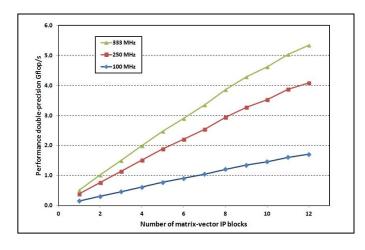

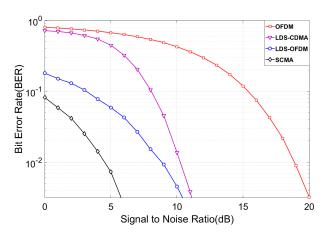

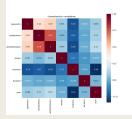

Timings are converted to execution rates in Gflop/s knowing that each 8x6 matrix-vector multiplication requires 2x8x6 flops; two operations, one addition and one multiplication, for each matrix element. The performance for the double precision matrix-vector kernel is shown in Fig. 2.

The speed-up for twelve blocks relative to one block is 10.5x representing a parallel efficiency of 94%. Scaling with clock speed is also good. With twelve matrix-vector blocks, the performance improves from 1.71 double precision GFlop/s at 100 MHz to 5.34 GFlop/s from at 333 MHz, an efficiency of 94%.

We note that matrix-vector multiplication (MVM) is much less computationally efficient than say matrix-matrix multiplication (MXM). For MXM the computational efficiency increases linearly with the matrix size, but for MVM it never increases beyond 0.25 flops/byte.

Fig. 2. Performance in GFlop/s of a double precision matrix-vector kernel on the Xilinx ZU9EG FPGA using from one to twelve matrix-vector IP blocks at different clock frequencies

We are limited to twelve IP blocks for this case, not by the resources available on the chip (number of logic gates etc.) but by the complexity of the design. Adding more IP blocks and the required supporting infrastructure causes violation of timing constraints within the design and failure to generate a bitstream.

There are three factors which determine and which limit the achieved performance for our matrix-vector kernel

- i. the performance in flops/cycle of an individual matrix-vector IP block

- ii. the number of matrix-vector IP blocks in the design

- iii. the clock frequency used to drive the Programmable Logic (PL), principally the matrix-vector blocks but also the associated blocks e.g. the BRAM blocks

The performance of an individual matrix-vector IP block is targeting a peak of 2 flops/cycle but is limited in practice due to overheads associated with data transfers and pipeline start-up costs, to 1.65 flops/cycle (according to the performance estimate of Vivado HLS). The number of IP blocks employed and the clock frequency of the PL are limited by timing constraints. In particular we would like to be able to exploit all the available logic of the FPGA, but find that in practice these timing constraints place a limitation which is more severe than the amount of resources required. In other words, for our application, timing constraints outweigh resource constraints.

An ideal or peak performance figure,  $P_0$ , for this design with twelve blocks running at 333 MHz would be 2 flops/cycle x 12 blocks x 333 MHz = 7.99 Gflop/s. The actual performance,  $P_a$ , may be obtained from the ideal performance by two efficiency factors, the single block efficiency, eff<sub>s</sub>, and the efficiency with which the blocks are combined in parallel in the design, eff<sub>p</sub>, thus:

$$P_a = P_0 x eff_s x eff_p = 5.34 Gflop/s$$

Assuming the performance estimate from Vivado HLS is realised in practice, gives a value for eff<sub>s</sub> of 85%, which implies the parallel efficiency figure for the design, eff<sub>p</sub>, is 79%.

There is a relationship, a trade-off, between the number of blocks and the maximum clock speed. For a simple design we can run the code at a higher clock speed, but as the number of matrix-vector blocks and memories increases, the complexity of the design increases and the maximum clock speed decreases. As the clock speed increases and/or the number of matrix-vector blocks increases, the design reaches a point at which timing constraints become important and timing violations cause the implementation to fail.

The maximum clock frequency at which the design operates correctly is shown in Table 1 for different numbers of matrix-vector blocks. The impact on performance is that, although increasing the number of blocks from one to twelve potentially delivers up to a twelve-fold increase in performance, the clock speed is reduced from 450 MHz to 333 MHz, a reduction of 74%, so the 12x potential increase is immediately limited to 8.9x.

TABLE I. MAXIMUM CLOCK FREQUENCY AT WHICH THE DESIGN OPERATES CORRECTLY FOR DIFFERENT NUMBERS OF MATRIX-VECTOR BLOCKS

| Number of<br>matrix-vector<br>blocks | Maximum clock<br>frequency (MHz) | Matrix-vector<br>performance<br>(Gflop/s) |

|--------------------------------------|----------------------------------|-------------------------------------------|

| 1                                    | 450                              | 0.688                                     |

| 4                                    | 400                              | 2.372                                     |

| 8                                    | 333                              | 3.863                                     |

| 12                                   | 333                              | 5.339                                     |

#### III. PORTING THE LFRIC WEATHER FORECAST CODE

Having established a methodology using the matrix-vector kernel, we have started to apply these techniques to the LFRic code itself. LFRic can be run in many configurations representing a range of weather and climate scenarios at low-, medium- and high-resolutions. In order to characterise the performance we ran and profiled a baroclinic test case, which has been developed by the Met Office as a part of their performance evaluation procedure [10]. The version of LFRic used for this work implements only parts of the scientific model, namely the dynamics and individual kernels. LFRic dynamics was still under development at the time of this work and important optimisations to its algorithmic performance such as provision of a multigrid preconditioner were not complete. Furthermore, additional science modules such as physics, ocean-coupling and data assimilation will also need to be addressed in the future.

Profiling this test case shows that most of the CPU time is spent in the Helmholtz solver that is used to compute the pressure. Two subroutines account for greater than 50% of the CPU time for this test case. Both of these subroutines spend most of their time performing double-precision matrix-vector multiplication within an outer loop which runs over the vertical levels within the atmosphere.

This Helmholtz kernel, apply\_hx\_variable\_code, has been offloaded to the FPGA. It consists of a series of matrix-vector multiplications and ancillary calculations on six input variables. The only difference in our methodology compared with the matrix-vector kernel is that this time we have written the ARM code in standard Fortran rather than C, in order to fit better with the LFRic programming model. This kernel, as with the matrix-vector kernel, has been implemented in a design with twelve IP blocks capable of running independently, thus exploiting spatial parallelism on the FPGA.

A key issue for the LFRic code in exploiting the acceleration potential of the FPGA, as with any accelerator, is reducing the overhead of transferring data between the host CPU and the FPGA. Thus it makes little sense to look at the performance of one small kernel in isolation where that performance will be dominated by data transfer costs. We

need to port a full workflow consisting of a sequence of kernels so that key data structures exist on the FPGA for long periods and ideally are created and used entirely in FGPA memory.

LFRic uses data decomposition across parallel multi-node clusters with halo exchanges between sub-domains carried out using MPI. A part of a workflow may therefore be represented as follows:

Kernel 1 Halo exchange for variable x1 Kernel 2 Halo exchange for variable x2 Kernel 3 Halo exchange for variable x3

In offloading a whole workflow it is therefore essential to take into account the MPI communications required for halo exchange. Initially the halo exchange will be carried out between host CPUs with data transferred to and from the FPGAs. We note that the amount of data involved for halo exchange is much smaller than the entire data arrays as only boundary data needs to be transferred. As a further optimization step, MPI communications will be available directly from FPGA to FPGA, using communications libraries under development in the EuroExa project.

#### REFERENCES

- Bacon, D.F., Rabbah, R. and Shukla, S., 2013. FPGA programming for the masses. Communications of the ACM, 56(4), pp.56-63

- [2] Gan, L., Fu, H., Yang, C., Luk, W., Xue, W., Mencer, O., Huang, X. and Yang, G., 2014, September. A highly-efficient and green data flow engine for solving euler atmospheric equations. In 2014 24th International Conference on Field Programmable Logic and Applications (FPL), pp. 1-6

- [3] L.F. Richardson, Weather Prediction by Numerical Process, Cambridge University Press, 1922

- [4] Science and Technology Select Committee (Commons), Session 2010-2012, 13th Report - Science in the Met Office - Volume I, HC 1538, 21 February 2012

- [5] Perrels, A., Th Frei, Francisco Espejo Gil, L. Jamin, and A. Thomalla. "Socio-economic benefits of weather and climate services in Europe." (2013)

- [6] Staniforth, A., Melvin, T. and Wood, N., 2013. Gungho! a new dynamical core for the unified model. In Proc. ECMWF Workshop on Recent Developments in Numerical Methods for Atmosphere and Ocean Modelling.

- [7] Adams AV, Ford RW, Hambley M, Hobson JM, Kavcic I, Maynard CM, Melvin T, Mueller EH, Mullerworth S, Porter AR, Rezny M. LFRic: Meeting the challenges of scalability and performance portability in Weather and Climate models. unpublished. arXiv preprint arXiv:1809.07267. 2018 Sep 19

- [8] Xilinx Inc., Vivado Design Suite User Guide: High-Level Synthesis, UG902 (v2017.2) June 7, 2017

- [9] Xilinx Inc. 2017. Zynq Ultrascale+ MPSoC. (2017) <a href="https://www.xilinx.com/products/silicon-devices/soc/zynq-ultrascale-mpsoc.html">https://www.xilinx.com/products/silicon-devices/soc/zynq-ultrascale-mpsoc.html</a>, accessed 7th February 2019

- [10] Christopher Maynard, Met Office, private communication

## Direct Communication between Distributed FPGA Resources

Joshua Lant

APT Group, Department of Computer Science

University of Manchetser

Manchester, UK

joshua.lant@manchetser.ac.uk

Javier Navaridas

APT Group, Department of Computer Science

University of Manchetser

Manchester, UK

javier.navaridas@manchetser.ac.uk

Abstract—In recent years the interest in the use of FPGA technology within HPC has been growing rapidly. Burgeoning application domains such as Deep Learning bring computational models which are much more suited to FPGA architectures, being able to take advantage of stream-like processing capabilities over distributed nodes. One of the key obstacles in the uptake of such systems is in the ability of the FPGA resources to act autonomously from the CPU. In this work we examine the progress that has been made in this domain, and compare it with our own work in decoupling the FPGA fabric from CPU resources for reliable network communications.

Index Terms—Interconnects, FPGA, Transport Layer, HPC.

#### I. INTRODUCTION

FPGAs have shown great promise for the next generation of HPC systems, owing to their strong performance and energy characteristics when faced with data-intensive workloads and stream-like processing. Traditionally shunned due to their difficult programmability and low off-chip memory bandwidth (vs. GPU), maturing ecosystems, larger on-chip memories and integrating advanced memory systems (e.g. HBM [1]) mean architects are now focusing on the potential of FPGAs in HPC/data-centre systems. This is being driven forward by very rapid advances in what is touted to be the FPGA's "killer app"; Deep Learning [2].

While GPUs remain the go-to accelerator due to their floating point performance and mature ecosystems, increasingly large systems such as those at Microsoft [3] and Amazon's AWS service are turning towards the FPGA in their datacenters to provide much higher performance-per-watt over GPUs, in a domain where power consumption is becoming an ever growing issue. There are numerous workloads which are shown to outperform the GPU in terms of power consumption. For example, in [4] it is shown that the FPGA can achieve similar performance to GPU on a number of the BLAS<sup>1</sup> routines, but achieving much higher energy efficiency. We believe that as tighter power constraints are placed upon HPC systems, we are likely to see the FPGA feature as a standard component of large heterogeneous HPC systems in the very near future, particularly given their ever maturing programming environments.

This work was funded by the European Union's Horizon 2020 research and innovation programme under grant agreements No 671553 and 754337.

Another particular advantage that the FPGA can find over GPU is the ability to utilize reduced precision, custom data types and fine grained parallelism to achieve greater performance. As an example, the feed-forward nature of much of the computation involved in Deep Neural Networks (DNNs), and the ability to take advantage of custom data-types and reduced precision [2], for example in binarized neural networks [5], makes the FPGA look like an ideal candidate for accelerating these types of workloads. This is because while GPUs are able to achieve massive parallelism at the thread level, the use of highly customized circuits over distributed FPGA resources offers a clear advantage. It allows for the exploitation of deeply pipelined architectures, naturally providing finer grained parallelism, and by utilizing distributed on-chip memory can offer higher performance for memory-bound operations [6].

#### II. THE NEED FOR DIRECT COMMUNICATION

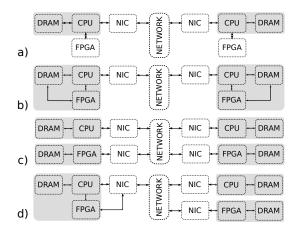

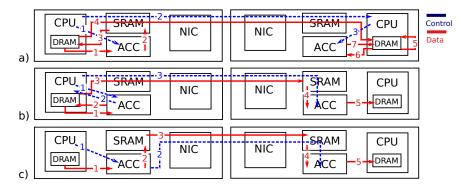

A key barrier in the development and exploitation of distributed FPGA resources within the context of the HPC systems is the traditional use of the FPGA as a mere coprocessor, loosely coupled to the CPU and network resources attached via PCIe or other equivalent bus-based interconnect (see Figure 1a ). Many examples of this sort of acceleration architecture exist; see [7]. Not only does this architectural model exacerbate the limited off-chip memory bandwidth of the FPGA by further distancing the accelerator from the main memory hierarchy of the CPU, but it severely limits the feasibility of data-flow processing between distributed FPGA resources. This is due to the dependence on the CPU for performing network transactions that is a result of the FPGA being seen merely as a peripheral device.

Modern FPGA architectures such as the Xilinx Zynq Ultrascale+, and the Intel Stratix 10, complete with integrated hard-core processors including IOMMUs allow for the configuration seen in Figure 1b, allowing shared memory and cache-coherence between the CPU and FPGA. While this tight coupling allows for lower latency transfers between local accelerator and memory, it does noting to aid the cumbersome software networking stack in being bypassed. Typical methods such as TCP/IP are required to provide reliable transfer of data between nodes, with costly data copies between network buffers etc.

<sup>1</sup>http://www.netlib.org/blas/

Fig. 1. Possible distributed FPGA System Configurations (top a - bottom d).

Like others have argued [8], we see that the remedy to the issue is to promote the FPGA resources to the status of a full peer within the network, capable of issuing its own reliable transactions into the network, as well as being able to process inbound network traffic directly. In enabling the FPGA to perform RDMA operations directly and offloading traditional networking stacks into hardware, i.e. TCP offloading, this gives rise to the configuration seen in Figure 1c. Here we see that the FPGA is now a peer within the network, and is fully disaggregated from the CPU resources, meaning that FPGA resources can be scaled without increasing the corresponding number of CPUs. However, in this setup the FPGA is unable to exploit a lower latency, shared memory model with other distributed memory spaces; a property which is vital for many workloads and for providing the FPGA better control of the data flow. All this is without mentioning the significant scalability and complexity issues associated with TCP offloading [9].

The solution we have proposed to this issue [10] is to create a NIC which sits in the fabric of the FPGA, and using a custom network protocol is able to utilize a simple geographic addressing scheme [11], where the target node addresses are seen simply as the upper regions of a fully global memory space. The NIC supports hardware primitives for both shared memory and RDMA communications, and the transport layer is fully offloaded into the hardware, bypassing the CPU completely for inter-FPGA data transfers. In doing this we are able to reach the configuration shown in Figure 1d, where the FPGA can act alone, as a fully disaggregated peer on the network, but can also write directly into a shared memory space between the CPU and other resources (local or remote). This opens up the possibility for fine grained acceleration across distributed FPGAs, providing maximum flexibility in the architecture.

#### III. RELATED WORK

Many attempts have been made by academics and industry alike over the past decade to put FPGA technology to work within a HPC or datacentre context. While much of the work on datacentre acceleration with FPGAs form the largest such systems, the radically differing requirements in terms of workload, reliability, bounds on jitter etc. mean that many of these solutions are not directly applicable, or must be modified for use in a general purpose HPC system.

Maxwell [12] is a proof of concept for a general purpose FPGA based supercomputer, comprising Intex Xeon CPUs and a total of 64 Xilinx FPGAs configured in a 2d torus, with CPUs and FPGA connected via PCI. This solution obviously suffers the many pitfalls discussed above, with regards to communication being directed through the CPU for network operations beyond a given scale, with only point to point connections between the FPGA for parallel communications. Other systems such as QP [13] use a similar approach, attaching the FPGA as a coprocessor via the PCI bus, forcing the FPGA to communicate through the CPU.

Novo-G# [14] is a system of multiple FPGAs and host CPU within a single server, with many of these servers comprising the entire system. While intra-server FPGAs can communicate directly with one another, inter-server communication must be made through the CPU via PCIe connections, and then via standard Gigabit Ethernet or Infiniband. This limitation means that direct communication between FPGAs is again limited in scale.

Other systems have been designed to use the system bus of the processor in order to couple them far more tightly with the memory system of the CPU. Systems such as the Cray XD-1 [15], which uses AMD's HyperTransport, and the work of Ling et al. at Intel [16] which use the Front-Side-Bus all provide this sort of architectural configuration, allowing for much higher throughput between system memory and accelerator. These architectures however still require the CPU to initiate network transfers, meaning that the use of dataflow style processing over multiple FPGAs is still inhibited by traditional networking techniques.

Recent work at IBM [17] has created a network attached FPGA system, which completely disaggregates the CPU from accelerator resources. This is done in order to allow CPU and FPGA resources to be scaled independently in datacentre environments. They use a hardware offloaded transport layer in order to allow the FPGA to communicate directly to the network. However, this means that all communication must traverse the full networking stack. There is no possibility to perform NUMA type accesses, and therefore tight coupling between the FPGA and CPU memory hierarchies is not possible.

Microsoft have created a system [3] which allows for FPGAs to communicate among themselves at the cloud scale. The FPGAs are situated as a *bump in the wire*, placed between the NIC and a Top-of-Rack switch, and are used for innetwork processing. They implement a lightweight transport layer in the fabric of the FPGA which supports TCP/IP, with which the FPGAs can communicate with one another. The main drawback with this architecture in regards to its use in a HPC context is the fact that CPUs still use the traditional software stack for TCP/IP protocols. Only the

Fig. 2. Control and data paths for a) software based TCP, b) custom software transport, c) our hardware offloaded solution.

FPGAs can communicate using this layer. Another issue is the fact that similarly this mechanism cannot be used for shared memory communications, providing only a method for RDMA transfers.

The poor latency of software implementations of TCP make this an undesirable solution in a HPC environment. While full hardware offloading of the TCP transport layer is possible to alleviate this latency issue, implementations are geared towards financial trading, where scalability is not a primary concern. Attempts have been made to solve this scalability issue, with [9] allowing for ≈10000 simultaneous connections. However this implementation is dreadfully wasteful of off-chip RAM resources, requiring around 1.3GB of memory to sustain these connections. Our solution offers a connectionless (datagram) approach, minimizing the state information required for the transport layer to perform reliable communications.

#### IV. OUR SOLUTION

Like some of the other works in this field, we regard the hardware offloading of the majority of the networking stack to be imperative for the FPGA to be disaggregated from the CPU resources, to elevate the status of the FPGA from an accelerator to a standalone element within the system. Given the requirements for reliability and the issues caused by packet dropping within a HPC context, this means that the whole transport layer must also be implemented within hardware. The best way we see to do this is to implement the Network Interface within the FPGA fabric. While this means that FPGA resources will be used for networking capabilities when they could be put to use for greater computing power, the burden is not too high within our system. By using a connectionless transport and keeping retransmission data for large transfers within external DRAM (rather than in retransmission buffers in the FPGA) we are able to achieve a modest area overhead in our implementation.

Our NIC contains two segregated data and control paths, one for shared memory transactions, and another for RDMA operations. In this manner the FPGA fabric is capable of writing shared memory operations directly to the NIC, enabling it to submit work directly to remote accelerators. Data can be written to a remote RAM using the DMA engine, and then

shared memory operations can be used to inform the remote accelerator that there is new data to be worked on.

The datapaths are segregated in the NIC because these two communication methods have very different requirements and properties. Due to the fact that the distributed shared-memory operations typically will be formed of small messages, used for control, management, synchronization etc. we store the data in the NIC as it is pushed to the network. In this way retransmission can be performed within the network and the latency of these operations is minimized.

Given that RDMA operations can consist of much larger data transfers, capable of saturating the link bandwidth, it is infeasible to store this data in the NIC for retransmission. Instead a method is sought which enables the NIC to track outstanding DMA operations which are unacknowledged, and enables it to directly rebuild partial transfers in the event of retransmission. The drawback of this method is that double buffering is required in the sender in the event that the user wishes to work on the data while the transfer is in progress, as the user has no knowledge on the status of a partial transfer. It is only informed when a full DMA transfer has completed successfully.

Figure 2 shows the benefits to the communication path when distributed FPGA resources are able to communicate among themselves with no CPU involvement. In Figure 2a we see the data copies and control information which needs to be transferred for a traditional software TCP stack. The TCP protocol requires copies of the data to be made and placed in send buffers for transfer, creating additional latency. In this instance we see that the data needs to be copied from the intermediate SRAM that the accelerator utilizes, back into main memory where the TCP buffers reside. A copy is also required between the receive buffers and userspace memory. Offloading of these buffers to hardware to be closer to the Network Interface would still require an additional copy stage, and would also use excessive memory resources (limiting the scalability of either the window size, or the number of concurrent TCP connections that can be kept track of). As well as this additional data copying, the remote CPU needs to be responsible for notifying the remote accelerator of work, requiring additional control information to be sent. Therefore additional latency is also seen as the local CPU cannot initialize work directly on the remote FPGA. Our solution alleviates this requirement by writing directly into memory, and using a geographic addressing scheme as a means to locate the destination node.

In Figure 2b we see a solution which utilizes our custom network protocol, but still uses a software based transport layer. In this instance we see that the local CPU is able to submit work directly to the remote accelerator using our direct shared-memory communication mechanism. However, the data to be transferred must still be copied back into DRAM by the accelerator in order for the transport layer to send it. This is because the CPU has no knowledge of the accelerator's work status, and the accelerator has no knowledge of the RDMA transfer status. Depending on how the reliability layer may be implemented, an additional memory copy may also be required to dedicated network send/receive buffers. This solution also results in additional communication requirements between the CPU and accelerator. As shown in the diagram, there is an additional stage of notification between the accelerator and CPU in the critical path, to inform the CPU that it has completed its work. This is not required if the accelerator can initiate network transfers itself.

In Figure 2c we see the data path for our hardware-offloaded solution. In this instance, once the accelerator has completed its work it issues an RDMA operation directly to the NIC, and then writes shared memory operations to the remote accelerator's work buffer, informing it that there is new work to be performed. Once this is completed then the remote accelerator notifies its local CPU that the work has been done and it has new data to process. As is shown, this solution is far more amenable to data-flow type processing, allowing for simpler pipelining of data through the distributed FPGA resources than in a traditional software approach.

While several other solutions [12], [18], allow for this sort of dataflow processing, it is typically performed using only point-to-point links between the FPGAs, limiting the topologies which can be created to tori/mesh topologies with direct nearest neighbour communication only. This in turn limits the scalability of the utilization of distributed FPGA resources to those located within a single rack, and limits the resilience of the system since these topologies mean that a node failure will necessarily affect the neighbouring nodes. When combined with our switch design [11], this solution allows for the creation of modern HPC topologies such as Jellyfish, Dragonfly and Fat-Trees.

#### V. CONCLUSIONS

In this paper we show that the needs of the network to enable reconfigurable HPC systems to reach their full potential are not being met by today's technologies. We argue that a fully hardware offloaded, connectionless transport layer is the only sensible way to allow for modern HPC communications (MPI and NUMA shared-memory type operations) to be performed directly in inter-FPGA or FPGA-remote CPU configurations. We show how our solution removes several

memory copies from a datflow scenario, bypassing the CPU for reliable inter-FPGA networking and better facilitating distributed FPGA acceleration.

#### REFERENCES

- G. Singh, "Xilinx 16nm datacenter device family within-package hbm and ccix interconnect," in 2017 IEEE Hot Chips 29 Symposium (HCS), pp. 1–22, IEEE, 2017.

- [2] E. Nurvitadhi, G. Venkatesh, J. Sim, D. Marr, R. Huang, J. Ong Gee Hock, Y. T. Liew, K. Srivatsan, D. Moss, S. Subhaschandra, et al., "Can fpgas beat gpus in accelerating next-generation deep neural networks?," in *Proceedings of the 2017 ACM/SIGDA International* Symposium on Field-Programmable Gate Arrays, pp. 5–14, ACM, 2017.

- [3] A. M. Caulfield, E. S. Chung, A. Putnam, H. Angepat, J. Fowers, M. Haselman, S. Heil, M. Humphrey, P. Kaur, J.-Y. Kim, et al., "A cloud-scale acceleration architecture," in *The 49th Annual IEEE/ACM International Symposium on Microarchitecture*, p. 7, IEEE Press, 2016.

- [4] S. Kestur, J. D. Davis, and O. Williams, "Blas comparison on fpga, cpu and gpu," in 2010 IEEE computer society annual symposium on VLSI, pp. 288–293, IEEE, 2010.

- [5] E. Nurvitadhi, D. Sheffield, J. Sim, A. Mishra, G. Venkatesh, and D. Marr, "Accelerating binarized neural networks: Comparison of fpga, cpu, gpu, and asic," in 2016 International Conference on Field-Programmable Technology (FPT), pp. 77–84, IEEE, 2016.

- [6] G. Lacey, G. W. Taylor, and S. Areibi, "Deep learning on fpgas: Past, present, and future," arXiv preprint arXiv:1602.04283, 2016.

- [7] C. Kachris and D. Soudris, "A survey on reconfigurable accelerators for cloud computing," in 2016 26th International conference on field programmable logic and applications (FPL), pp. 1–10, IEEE, 2016.

- [8] K. D. Underwood, K. S. Hemmert, and C. D. Ulmer, "From silicon to science: The long road to production reconfigurable supercomputing," ACM Transactions on Reconfigurable Technology and Systems (TRETS), vol. 2, no. 4, p. 26, 2009.

- [9] D. Sidler, G. Alonso, M. Blott, K. Karras, K. Vissers, and R. Carley, "Scalable 10gbps tcp/ip stack architecture for reconfigurable hardware," in Field-Programmable Custom Computing Machines (FCCM), 2015 IEEE 23rd Annual International Symposium on, pp. 36–43, IEEE, 2015.

- [10] J. Lant, C. Concatto, A. Attwood, J. A. Pascual, M. Ashworth, J. Navaridas, M. Luján, and J. Goodacre, "Enabling shared memory communication in networks of mpsocs," *Concurrency and Computation:* Practice and Experience, p. e4774.

- [11] C. Concatto, J. A. Pascual, J. Navaridas, J. Lant, A. Attwood, M. Lujan, and J. Goodacre, "A cam-free exascalable hpc router for low-energy communications," in *International Conference on Architecture of Computing Systems*, pp. 99–111, Springer, 2018.

- [12] R. Baxter, S. Booth, M. Bull, G. Cawood, J. Perry, M. Parsons, A. Simpson, A. Trew, A. McCormick, G. Smart, et al., "Maxwell-a 64 fpga supercomputer," in Second NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2007), pp. 287–294, IEEE, 2007.

- [13] M. Showerman, J. Enos, A. Pant, V. Kindratenko, C. Steffen, R. Pennington, W.-m. Hwu, et al., "Qp: A heterogeneous multi-accelerator cluster," in Proc. 10th LCI International Conference on High-Performance Clustered Computing, 2009.

- [14] A. D. George, M. C. Herbordt, H. Lam, A. G. Lawande, J. Sheng, and C. Yang, "Novo-g#: Large-scale reconfigurable computing with direct and programmable interconnects," in 2016 IEEE High Performance Extreme Computing Conference (HPEC), pp. 1–7, IEEE, 2016.

- [15] Cray User Group, "The cray xd1 technical overview." https://cug.org/5-publications/proceedings\_attendee\_lists/2004CD/S04\_Proceedings/pages/Authors/Shan\_Amar\_Slides.pdf, 2004.

- [16] L. Ling, N. Oliver, C. Bhushan, W. Qigang, A. Chen, S. Wenbo, Y. Zhihong, A. Sheiman, I. McCallum, J. Grecco, et al., "Highperformance, energy-efficient platforms using in-socket fpga accelerators," in Proceedings of the ACM/SIGDA international symposium on Field programmable gate arrays, pp. 261–264, ACM, 2009.

- [17] J. Weerasinghe, R. Polig, F. Abel, and C. Hagleitner, "Network-attached fpgas for data center applications," in 2016 International Conference on Field-Programmable Technology (FPT), pp. 36–43, IEEE, 2016.

- [18] A. Putnam, A. M. Caulfield, E. S. Chung, D. Chiou, K. Constantinides, J. Demme, H. Esmaeilzadeh, J. Fowers, G. P. Gopal, J. Gray, et al., "A reconfigurable fabric for accelerating large-scale datacenter services," ACM SIGARCH Computer Architecture News, vol. 42, no. 3, pp. 13– 24, 2014.

## Event-based computation: Unsupervised elementary motion decomposition

#### Petrut A. Bogdan School of Computer Science The University of Manchester Manchester, UK

petrut.bogdan@manchester.ac.uk

#### Michael Hopkins

School of Computer Science

The University of Manchester

Manchester, UK

michael.hopkins@manchester.ac.uk

#### Garibaldi Pineda García School of Engineering and Informatics University of Sussex Brighton, UK

g.pineda-garcia@sussex.ac.uk

#### Robert James

School of Computer Science The University of Manchester Manchester, UK robert.james@manchester.ac.uk

### Simon Davidson

School of Computer Science

The University of Manchester

Manchester, UK

simon.davidson@manchester.ac.uk

#### Steve B. Furber

School of Computer Science The University of Manchester Manchester, UK steve.furber@manchester.ac.uk

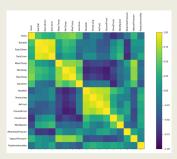

Abstract—Fast, localised motion detection is crucial for an efficient attention mechanism. We show that modelling a network capable of such motion detection can be performed using spiking neural networks simulated on many-core neuromorphic hardware. Moreover, highly sensitive neurons arise from the presented network architecture through unsupervised self-organisation. We use a synaptic rewiring rule which has been shown to enable the formation and refinement of neural topographic maps. Our extension allows newly formed synapses to be initialised with a delay drawn from a uniform distribution. Repeated exposure to moving bars enables neurons to be sensitised to a preferred direction of movement. Incorporating heterogeneous delays results in more sensitive neural responses. A readout mechanism involving a neuron for each learnt motion is sufficient to establish the input stimulus class.

*Index Terms*—SpiNNaker, Neuromorphic computing, Spiking Neural Network, structural plasticity, synaptic rewiring, topographic maps

#### I. INTRODUCTION

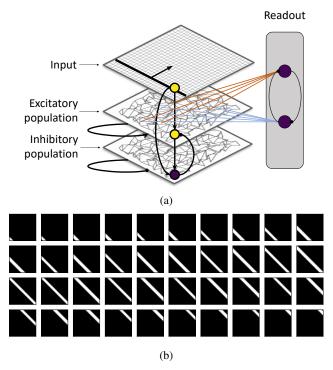

Neuromorphic platforms are relatively novel computational systems designed to mimic key aspects of mammalian brain operation: massive parallelism, low energy consumption, fault tolerance and sparsity. These platforms come in multiple flavours ranging from full-custom chip design (mixed analogue-digital [1] and fully digital designs [2]) to using a vast array of off-the-shelf components. SpiNNaker [3] (the full system is pictured in Fig. 1) is a digital many-core neuromorphic platform designed to simulate a vast number of biologically-inspired spiking neurons in real time.

Novel computing architectures require the development of new methodologies and tools to harness their full capabilities.

The design and construction of the SpiNNaker machine was supported by EPSRC (the UK Engineering and Physical Sciences Research Council) under grants EP/D07908X/1 and EP/G015740/1, in collaboration with the universities of Southampton, Cambridge and Sheffield and with industry partners ARM Ltd, Silistix Ltd and Thales. Ongoing development of the software is supported by the EU ICT Flagship Human Brain Project (H2020 785907), in collaboration with many university and industry partners across the EU and beyond.

Fig. 1: The 1 million ARM-core SpiNNaker machine. Capable of simulating on the order of 200 million neurons, with 1,000 synapses each, in real-time.

While using ARM technology for the 18 computational cores present on chip, SpiNNaker has been designed specifically for spiking neural network (SNN) simulations using a purposebuilt router and attaching small amounts of fast memory to each individual core.

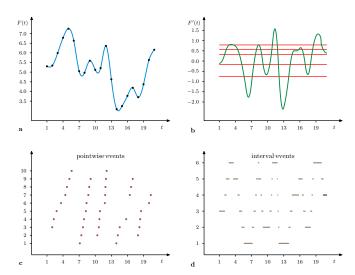

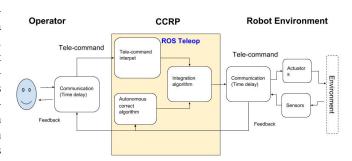

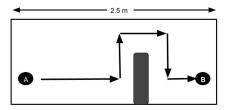

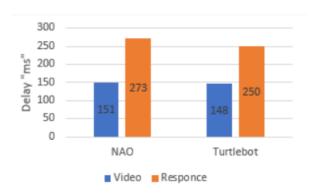

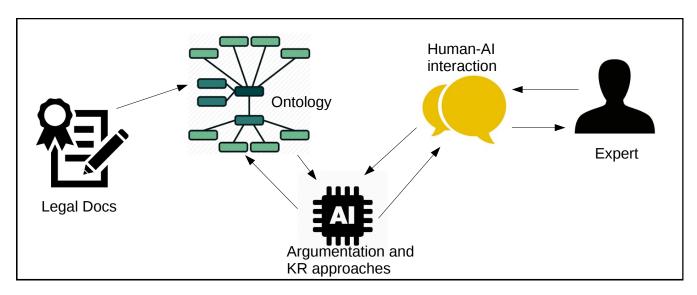

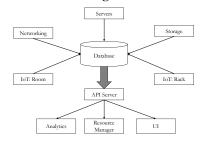

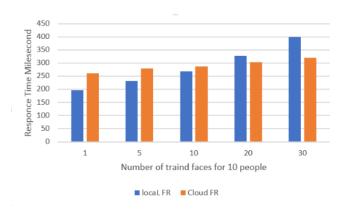

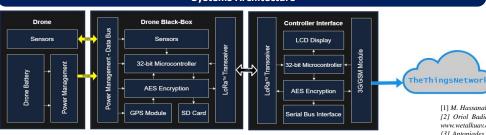

We build on previous work [4] and present an end-to-end approach to perform elementary motion decomposition using leaky integrate-and-fire neurons and structural and synaptic plasticity [5]. Further, the computational platform which is the basis for these simulations is event-driven [6], including the spiking visual input provided to the network. The biologically inspired sensory processing method presented here is an alternative to traditional frame-based computer vision.