## Energy-performance tradeoffs for HPC applications on high-end and low power systems

Enrico Calore, Alessandro Gabbana, Sebastiano Fabio Schifano, Raffaele Tripiccione

INFN and Università degli Studi di Ferrara, Ferrara, Italy

## Abstract

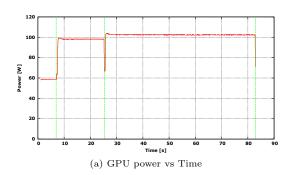

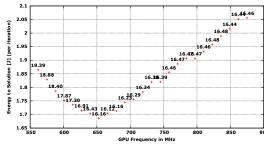

Energy efficiency is becoming more and more important in the HPC field; high-end processors are quickly evolving towards more advanced power-saving and power-monitoring technologies. At the same time, lowpower processors, designed for the mobile market, attract interest in the HPC area for their increasing computing capabilities, competitive pricing and low power consumption. In this work we compare energy and computing performances of different architectures, including low-power and high-end HPC systems. As a benchmark we use an HPC Lattice Boltzmann application which has been instrumented with several software and hardware tools in order to monitor its power consumption while running on different systems. We run this application on the ARM Cortex-A15 CPU [1] and on the GK20A GPU of a Tegra k1, as well as on an ARM Cortex-A53 and on high-end systems such us Intel Haswell CPUs [2] and NVIDIA K80 GPUs. Our analysis uses time-accurate measurements, obtained by a simple custom-developed current monitor [3] and by hardware counters read by the PAPI library [4]. We discuss several energy and performance metrics, evaluating the different energy-performance tradeoffs available on the tested architectures. In Fig. 1a we show a typical plot of the measured power consumption of our benchmark with respect to the execution time (in this case measured on a K80 GPUs), while in Fig. 1b we show a plot of the energy-to-solution derived from several run performed with different hardware/software parameters (in this case changing the GPU frequency). Such derived plots, produced for different hardware architectures, shed light on the different trade-off opportunities between computing capabilities and energy efficiencies.

(b) Energy to Solution vs GPU Frequency; Time to Solution as labels  $\,$

## References

- [1] M. Laurenzano, A. Tiwari, A. Jundt, J. Peraza, W. J. Ward, R. Campbell, and L. Carrington, "Characterizing the Performance-Energy Tradeoff of Small ARM Cores in HPC Computation," in *Euro-Par 2014 Parallel Processing*, ser. LNCS, 2014, vol. 8632, pp. 124–137.

- [2] D. Hackenberg, R. Schone, T. Ilsche, D. Molka, J. Schuchart, and R. Geyer, "An energy efficiency feature survey of the intel haswell processor," in *Parallel and Distributed Processing Symposium Workshop (IPDPSW)*, 2015 IEEE International, May 2015, pp. 896–904.

- [3] E. Calore, S. Schifano, and R. Tripiccione, "Energy-Performance Tradeoffs for HPC Applications on Low Power Processors," in *Euro-Par 2015: Parallel Processing Workshops*, ser. LNCS, 2015, vol. 9523, p. 737–748.

- [4] V. Weaver, M. Johnson, K. Kasichayanula, J. Ralph, P. Luszczek, D. Terpstra, and S. Moore, "Measuring energy and power with PAPI," in *Parallel Processing Workshops (ICPPW)*, 2012 41st International Conference on, 2012, pp. 262–268.